# Energy Storage System of the Converted Discharge Energy under VLF Testing Conditions

# **Master Thesis**

In partial fulfillment of the requirements for the degree

"Master of Science in Engineering"

Study program:

**Mechatronics**

FH Vorarlberg Vorarlberg University of Applied Sciences

Supervisor:

DI Dr. André Mitterbacher

Author:

Maximilian Preiss, B.Sc. 2010246009

# **Declaration in Lieu of Oath**

| "I nereby declare, under oath, | , that this master thesis has bee | n my independent work      |

|--------------------------------|-----------------------------------|----------------------------|

| and has not been aided with a  | any prohibited means. I declare,  | to the best of my knowl-   |

| edge and belief, that all pass | ages taken from published and     | unpublished sources or     |

| docments have been reprodu     | ced whether as original, slightly | changed or in thought,     |

|                                | ch at the corresponding placeso   | f the thesis, by citation, |

| where the extend of the origin | al quotes is indicated."          |                            |

|                                |                                   |                            |

|                                |                                   |                            |

|                                |                                   |                            |

|                                |                                   |                            |

|                                |                                   |                            |

| Place, Date                    |                                   | Signature                  |

# **Acknowledgement**

My main thanks go to my supervisor DI Markus Kostner from Baur GmbH and DI Dr. Andre Mitterbacher from the University of applied Science Vorarlberg for their critical and helpful suggestions during the whole process of this thesis. Especially their motivation and enthusiasm whenever I need help or advice in difficult situations helps me a lot to continue. I would also like to thank my working mates and friends for supporting me during the whole project time and giving me new input suggestions whenever I need it. This makes it much easier for me to continue, to plan the next steps, and not to lose the belief and always think positive.

Finally, I would like to thank all my family, especially a big thank you to my girlfriend Nina who always believes in me, supports me and stands by my side when I think I am stuck.

# Kurzfassung

Hochspannungskabel spielen in Stromverteilungsnetzen eine bedeutende Rolle. Isolationsfehler in Kabeln verursachen negative Auswirkungen auf das Betriebsverhalten. Anhand einer Wechselspannungsprüfung mit einem niederfrequenten Hochspannungsgenerator, erfolgt die Beurteilung der Isolationsqualität. Diese Generatoren erzeugen dafür eine sinusförmige Prüfspannungen von  $0.1 \rm Hz$  mit Spannungswerten bis zu  $65 \rm kV$ . Während der Qualitätsprüfung wird das Kabel wiederholt geladen und entladen. Der Entladevorgang am Kabel erfolgt über einen Entladekreis, in dem die Energie thermisch abgeleitet wird. Um diese Energie elektrisch wieder zu nutzen, soll eine neuartige Erweiterung in Form eines Energiespeichersystems vorgestellt werden.

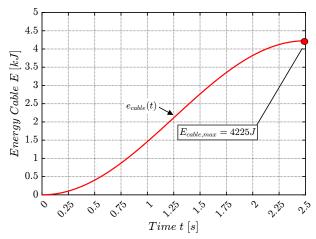

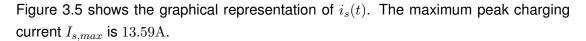

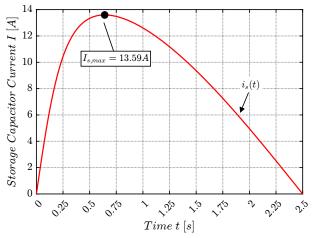

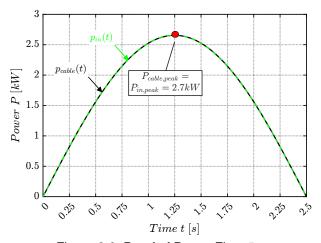

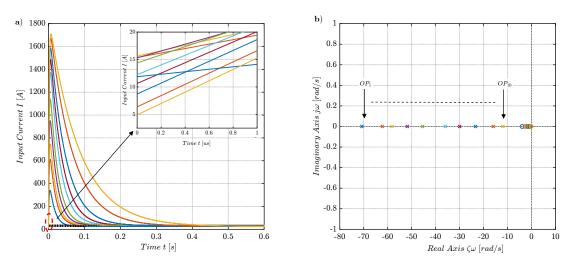

Diese Arbeit beschreibt den Designprozess eines Energiespeichersystems, das die Zwischenspeicherung der Entladeenergie ermöglicht. Das entwickelte System besteht aus einem bidirektionalen DC/DC-Wandler und einem Aluminium-Elektrolytkondensator. Der Energiespeicher ist auf die maximale Generatorleistung dimensioniert. Die effektive Regelung des Leistungsflusses zwischen Speichersystem und der verfügbaren Entladeenergie, erfolgt durch einen synchronen Buck-Boost Wandler. Zusammen mit einer theoretischen Analyse der zugrundeliegenden Problemstellung und der Anwendung von Wandler Analysemethoden, wurde die Dimensionierung des Wandlers durchgeführt. Darüber hinaus wurde ein Zustandsraummodell erstellt, um das Regelungssystem zu entwerfen. Implementiert ist eine Eingangsstromregelung anhand eines PI-Reglers. Die Bewertung des Systems erfolgt durch eine modellbasierte Hardware-Implementierung in Matlab Simulink und Plecs Blockset. Das System ist in der Lage. Entladeenergien von bis zu 4.3kJ in einer kurzen Ladezeit von 2.5s zwischenzuspeichern. Die maximale Spitzenleistung während der Ladephase beträgt 2.7kW. Basierend auf einer C-Code-Implementierung des digitalen Reglers, erfolgt eine hardwarenahe Simulationsstudie. Während des Designprozesses wurden theoretische Berechnungen durchgeführt. Diese zeigen, dass der Entwurf eines Speichermediums einen direkten Einfluss auf die Spitzenströme des Systems haben und auch die zulässigen Gleichspannungsbereiche der elektrischen Komponenten einschränken. Das entwickelte Energiespeichersystem und die Strategie zur Leistungsflussregulierung wurden durch Simulationsstudien untersucht. Die Ergebnisse zeigen eine ordnungsgemäße Ladephase des Speichersystems. Zusätzlich wurde eine Aussage über deren technische Machbarkeit getroffen.

Zusammenfassend stellt diese Arbeit einen detaillierten Entwurfsprozess des Energiespeichersystems vor. Dieser Designprozess sowie deren Machbarkeitsstudie soll für die weitere Ausarbeitung der Systemintegration dienen.

**Schlagwörter:** Energiespeicher System, Aluminium-Elektrolytkondensator, DC/DC Leistungswandler, Buck-boost Wandler, Digitaler Regelkreis

### **Abstract**

Power cables play an important role in power grids. Insulation faults in cables can have adverse effects on the operating behaviour. These effects can be assessed through an AC withstand test by using a very-low frequency high voltage generator. This generator produces a sinusoidal voltage waveform at  $0.1 \rm Hz$  with high voltage levels up to  $65 \rm kV$  peak. During the quality assessment, the power cable is repeatedly charged and discharged. The discharging process is done by a discharging circuit where the energy is dissipated thermally. But to reuse the dissipated energy a novel extension in form of an energy storage system is presented.

This thesis, therefore, describes the design process of an energy storage system that allows the temporary storage of the discharge energy. The developed system is composed of a bidirectional DC/DC converter and an aluminium electrolytic capacitor as storage type. Based on the maximum VLF system ratings the energy storage unit is dimensioned and sized. The effective power flow control between the storage system and the available discharge energy is done by a synchronous buck-boost converter. This bidirectional converter works in continuous conduction mode over the complete charging phase. Together with a theoretical analysis of the underlying problem and the use of converter analysis methods the selected synchronous buck-boost converter is dimensioned and sized. In addition, a state space AC modeling of the converter with its electrical uncertainties is conducted. With the converters AC model, the controller is designed. A closed-loop input converter current control scheme based on a proportional-integral controller is implemented. The system assessment is done by a model-based hardware implementation in Matlab Simulink and Plecs Blockset. The system is rated to store discharge energies up to 4.3kJ in a short charging period of 2.5s. The maximum peak power during the charging phase is 2.7kW. The digital proportional-integral controller is implemented through an emulation process of the designed analog controller. Based on a C-code implementation of the digital controller the gap between the real hardware is reduced. During the design process theoretical calculations are made and reveal that designing a capacitor storage unit has a direct impact on the peak system currents and also impose also limitations on permissible DC voltage ranges on electrical components. The developed energy storage system and its power flow control strategy were investigated through simulation studies. The results show proper charging of the energy storage medium. In addition, also a statement of the final technical feasibility is made.

In total, this work summarizes a detailed design process of the energy storage system. This proof of concept is intended to further advance the system integration.

**Keywords:** Energy storage system, aluminium electrolytic capacitor, DC/DC power converter, buck-boost converter, digital control strategy

# **Contents**

| 1 | intro | oductio | n                                                               | 1  |

|---|-------|---------|-----------------------------------------------------------------|----|

|   | 1.1   | Stater  | ment of the Problem                                             | 2  |

|   | 1.2   | Motiva  | ation                                                           | 5  |

|   | 1.3   | State   | of the Art                                                      | 6  |

|   | 1.4   | Object  | tives of this Thesis                                            | 7  |

|   | 1.5   | Syster  | m Requirements                                                  | 7  |

|   |       | 1.5.1   | Requirements Energy Storage Type                                | 8  |

|   |       | 1.5.2   | Requirements Converter Topology                                 | Š  |

|   | 1.6   | Struct  | ure of the Thesis                                               | 10 |

| 2 | Con   | cept    |                                                                 | 11 |

|   | 2.1   | Select  | tion of Suitable Energy Storage                                 | 11 |

|   |       | 2.1.1   | Evaluation Criteria                                             | 12 |

|   |       | 2.1.2   | Aluminium Electrolytic Capacitor                                | 13 |

|   |       | 2.1.3   | Supercapacitor                                                  | 14 |

|   | 2.2   | Utility | Analysis                                                        | 16 |

|   |       | 2.2.1   | Summary Energy Storage System                                   | 18 |

|   | 2.3   | Select  | tion of a DC/DC Converter Topology                              | 19 |

|   |       | 2.3.1   | Evaluation Criteria DC/DC Converter                             | 20 |

|   |       | 2.3.2   | Synchronous Buck-Boost Converter                                | 21 |

|   |       | 2.3.3   | Cuk - Converter                                                 | 23 |

|   |       | 2.3.4   | Sepic - Converter                                               | 24 |

|   |       | 2.3.5   | Utility Analysis DC/DC Converter                                | 25 |

|   |       | 2.3.6   | Summary Converter System                                        | 25 |

|   |       | 2.3.7   | Summary Concept Phase                                           | 27 |

| 3 | Sys   | tem De  | esign                                                           | 28 |

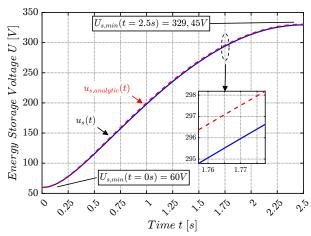

|   | 3.1   | •       | y Storage System Design                                         | 28 |

|   |       | 3.1.1   | Calculation and Selection of the Energy Storage Capacitor       | 28 |

|   |       | 3.1.2   | Selection and Sizing of Aluminium Electrolytic Capacitor Bank . | 30 |

|   |       | 3.1.3   | Comparison Aluminium Electrolytic Capacitor Bank with Super-    |    |

|   |       |         | capacitor Bank                                                  | 32 |

|   |       | 3.1.4   | Summary of Calculation and Selection of the Energy Storage Ca-  |    |

|   |       |         | pacitor                                                         | 34 |

|   | 3.2 | Analyt  | ical Calculation of the Energy Charging Process                  | 35  |

|---|-----|---------|------------------------------------------------------------------|-----|

|   |     | 3.2.1   | Summary Analytical Calculation                                   | 39  |

|   | 3.3 | Synch   | ronous Buck-Boost Converter                                      | 40  |

|   |     | 3.3.1   | Selection of the Operating Principle                             | 40  |

|   |     | 3.3.2   | Functional Converter Principle                                   | 41  |

|   |     | 3.3.3   | Steady State Analysis                                            | 43  |

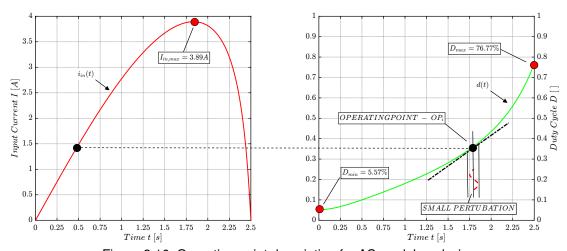

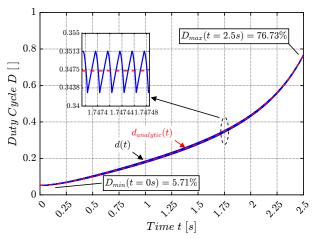

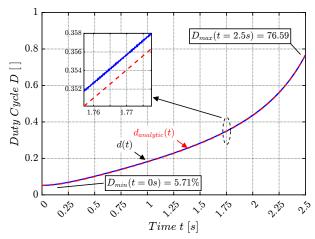

|   |     | 3.3.4   | Analytic Duty Cycle over Time of Synchronous Buck-Boost Con-     |     |

|   |     |         | verter                                                           | 46  |

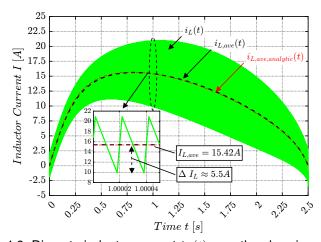

|   |     | 3.3.5   | Analytic Inductor Current over Time of Synchronous Buck-Boost    |     |

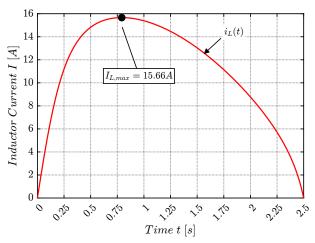

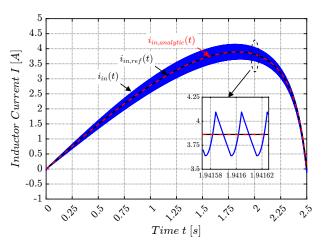

|   |     |         | Converter                                                        | 47  |

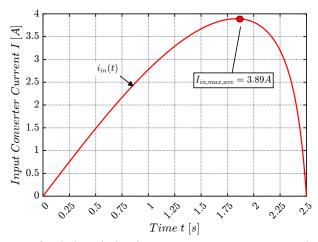

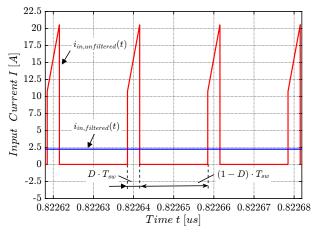

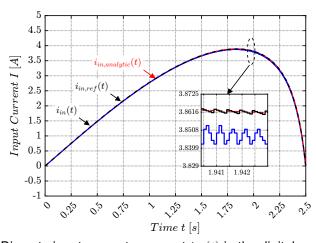

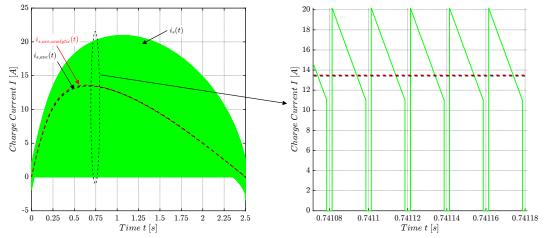

|   |     | 3.3.6   | Analytic Input Current over Time of Synchronous Buck-Boost       |     |

|   |     |         | Converter                                                        | 48  |

|   |     | 3.3.7   | Summary Theoretical Charging Process                             | 49  |

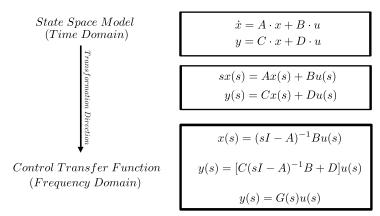

|   |     | 3.3.8   | State-Space-Averaging-Modeling                                   | 50  |

|   |     | 3.3.9   | Summary Synchronous Buck-Boost AC-Model                          | 56  |

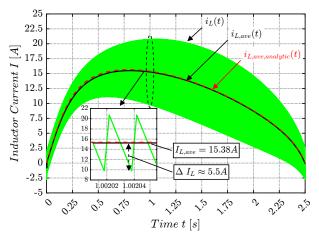

|   |     | 3.3.10  | Inductor Current Value Calculation                               | 57  |

|   |     | 3.3.11  | Calculation of Maximal Averaged Inductor Current                 | 57  |

|   |     | 3.3.12  | Inductor Design                                                  | 58  |

|   |     | 3.3.13  | Summary of Inductor Design                                       | 64  |

|   |     | 3.3.14  | MOSFET Design                                                    | 65  |

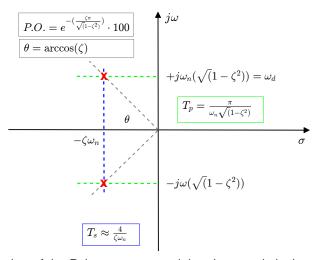

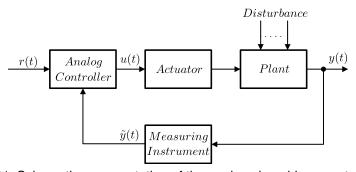

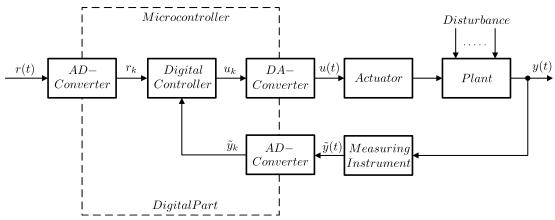

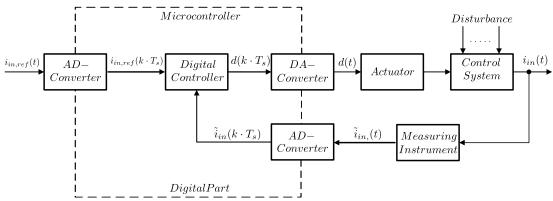

|   | 3.4 | Contro  | ol Engineering Design                                            | 72  |

|   |     | 3.4.1   | Definition of the Control Variable and the Control System        | 72  |

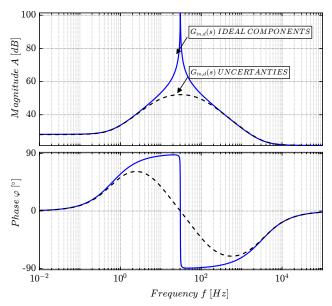

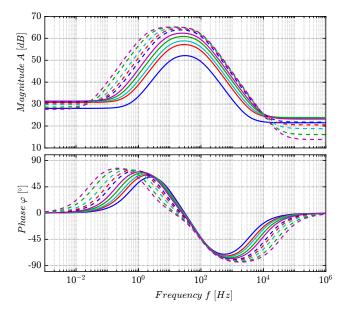

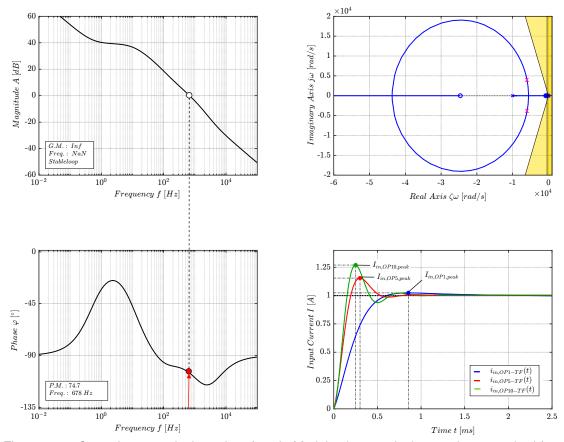

|   |     | 3.4.2   | Control Transfer Function Analysis                               | 72  |

|   |     | 3.4.3   | Summary from the Analysis of the Control Function System Be-     |     |

|   |     |         | haviour                                                          | 81  |

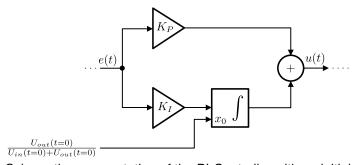

|   |     | 3.4.4   | Determination of the Control Structure                           | 82  |

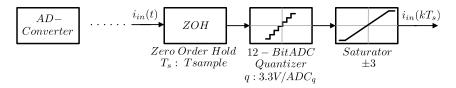

|   |     | 3.4.5   | Current Sensing Design                                           | 84  |

|   |     | 3.4.6   | Filter Design                                                    | 84  |

|   |     | 3.4.7   | Continuous Closed-Loop Input Current Control System of Syn-      |     |

|   |     |         | chronous Buck-Boost Converter                                    | 86  |

|   |     | 3.4.8   | Summary of the Continuous Closed-loop Input Current Control      |     |

|   |     |         | System                                                           | 89  |

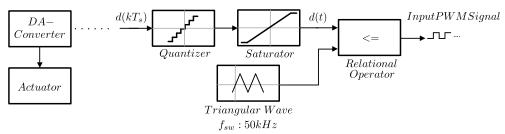

|   |     | 3.4.9   | Discretization of the Continuous-time PI-Controller              | 90  |

|   | 3.5 | Model   | -Based Hardware Implementation                                   | 91  |

|   |     | 3.5.1   | Bill of Material                                                 | 95  |

| ļ | Exp | erimen  | tal Simulation Evaluation of the Energy Storage System           | 98  |

|   | 4.1 | Verific | ation of the Converter System under DC/DC Operation              | 98  |

|   |     | 4.1.1   | Verfification with Continuous Time Controller                    | 98  |

|   | 4.2 | Verific | ation of the Charging Process under Variable Quantity Conditions | 101 |

|   |     | 4.2.1   | Verification with Continuous Time Controller                     | 101 |

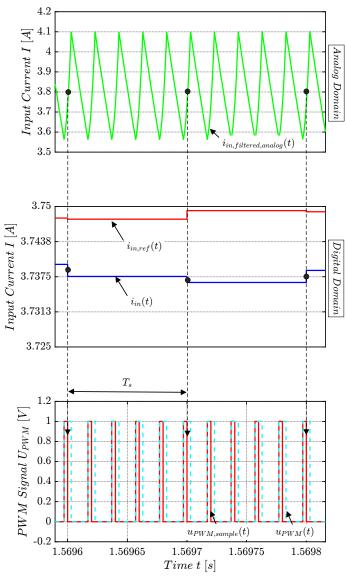

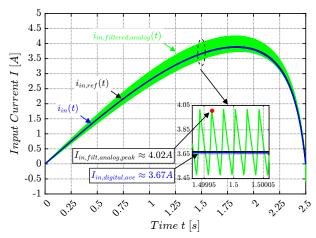

|   |     | 4.2.2   | Verification with Discrete Time Controller                       | 103 |

|   |     | 4.2.3   | Verification Power Dissipation at the Shunt Resistor             | 107 |

|   |     |         |                                                                  |     |

|    |       | 4.2.4 Verification Sensed Input Current to Reference Input Current | 108 |

|----|-------|--------------------------------------------------------------------|-----|

|    | 4.3   | Summary Experimental Verification                                  | 109 |

| 5  | Sun   | nmary and Outlook                                                  | 110 |

|    | 5.1   | Summary                                                            | 110 |

|    | 5.2   | Outlook                                                            | 112 |

| Bi | bliog | ıraphy                                                             | IX  |

| Li | st of | Figures                                                            | XII |

| Li | st of | Tables                                                             | XVI |

# 1 Introduction

Energy storage systems (ESS) are getting more and more attention in recent years. Through the set of methods and technologies which are nowadays used, different energy forms can be stored intermediately. This allows to access the stored energy at a later time and with the objective of reuse in a purposeful application, whenever it is needed.

One of the prime examples is renewable energy sources, such as wind, solar or photovoltaic. But due to their strong discontinuity in energy production and in some aspects their non-direct use of the available energy, leads exactly to the result that energy storing systems are required [1].

In addition to the above well known example, it should be mentioned that energy can be also available in other various forms as like electricity. For instance, radiation, chemical energy, gravitational potential and kinetic energy are building only a few of other energy sources. These energy sources can be stored in different energy storage types which are classified by their physical acting domain. A recently published review about energy storage types with their applications and recent developments are given in [2].

By using power electronics, the energy transfer for the intermediate ESS can be realized. However, together with the choice of storage type, this still involves several dependencies such as application, system integration, and the availability of the energy source over time. To illustrate the above statement, another commercially widely used principle for energy storage in electric vehicles is presented. Batteries and supercapacitors are frequently used for this purpose. Here, recuperation forms a central mechanism of energy provision. In their function, batteries and supercapacitors form a hybrid storage concept. This hybrid storage concept combines the advantages of both storage types. The electric drive system is used to recover the energy by switching into the generator mode. A bidirectional power converter transfers the provided power flow to the storage type. An overview of the state of the art in recuperation is given in the article [3].

Due to the strong growing attention to energy storage systems in today's technical applications as shown in electric vehicles and smart grid use, various benefits are ensured [2]. On the one hand, the electrical energy losses in electrical systems can be reduced while on the other hand reducing voltage fluctuations, improving power quality and increasing reliability as well as improving energy efficiency are only a few further positive aspects. However, despite all the advantages that an energy storage system brings,

there are some crucial problems such as controllability, changeability, and stability itself of the underlying power and energy demand.

These challenges lead engineers to develop stable energy storage systems that manage power and energy flow in an optimal manner. Generally, an ESS is categorized in a charging and discharging period. The first mentioned charging phase is done whenever energy is realized in any way and means, for example, electrical dissipation energy or kinetic energy during recuperation. The discharge phase is then used primarily in defined, targeted application scenarios to make the stored energy available. Such use cases can be to optimally overcome power peaks shaving or prevent the probability of failure of the device as it is presented in [4].

Based on these initial findings and the dependencies between energy storage topology and power electronics, a closer look will be taken at the stated problem. Based on the conceptual formulation, of the energy storage system which shall be developed a more detailed examination can be performed.

## 1.1 Statement of the Problem

In order to specifically address the problem of this thesis in concrete terms, a brief insight view of the general situation must be presented. This thesis stays in contact with a diagnostic system called a very-low frequency (VLF) generator, which can be used to assess the insulation quality in power cables. Now, subsequently, a step-by-step introduction to the problem follows. In the first part, the basic mechanisms of the underlying diagnostic system is presented. In further steps then the underlying problem and the transition to the energy storage system are then clarified.

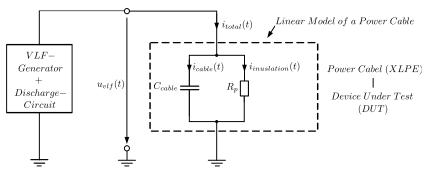

Power cables play an important role in energy distribution networks. The most commonly used cables are XLPE cables [5]. In the meanwhile, insulation failures of cables have become a severe safety hazard. Through the use of a VLF high voltage generator, an AC withstand test can be performed, to assess the quality of the power cable. In Figure 1.1 a simplified structure of a VLF test system with the device under test (DUT) is shown. The specimen under test can be described as a linear model with isolation consisting of a parallel connection between the cable capacitance  $C_{cable}$  and a high ohmic insulation resistor  $R_p$ . For an ideal cable,  $R_p$  is infinite. The quality measurement that is taken is referred to loss factor  $(\tan \delta)$ .

Figure 1.1: Schematic structure of a VLF AC withstand testing application where on the left side the VLF generator is accommodated and on the right side the simple equivalent circuit model of a power cable (DUT) is seen

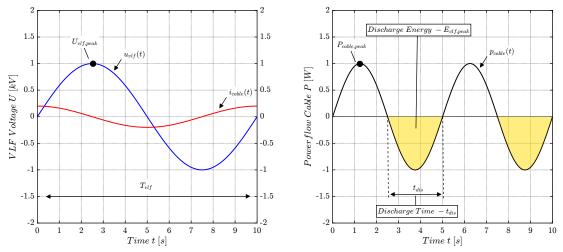

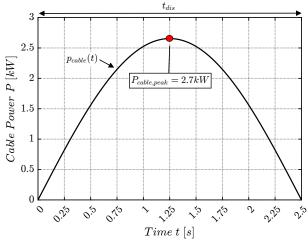

With the use of the generated VLF sinusoidal waveform (Parameters:  $f_{vlf}=0.1{\rm Hz}$ ) the AC withstand test is carried out. In Figure 1.2 the very-low frequency test voltage  $u_{vlf}(t)$  of the generator under ideal power cable conditions is shown. Hereby, the signal curves  $u_{vlf}(t)$ ,  $i_{cable}(t)$  and  $p_{cable}(t)$  are demonstrated only to reflect the signal characteristics during testing and are therefore not truthfully deposited. The resulting power flow  $p_{cable}(t)$  is shown on the left which has the double frequency of  $u_{vlf}(t)$ .

Figure 1.2: Very-low frequency test voltage of a VLF high voltage generator in order to assess the insulation quality  $\tan \delta$  of a power cable

It can be recognized that during a measurement period  $T_{vlf}$  the system passes two phases, according to its resulting power flow  $p_{cable}(t)$ . In each half-wave of  $u_{vlf}(t)$ , the power cable is charged and discharged. The discharge phases of the stored energy can be therefore attributed to quadrants two and four of the VLF sinusoidal voltage. The generator setup consists in its structure of a high voltage cascade ([6]) to produce the VLF test voltage while due to the discharge phase a discharging circuit is necessary. By decoupling the charging and discharging phase, the discharge energy can be separately thermally dissipated. The evaluation of the  $\tan \delta$  is then done after each VLF period. Due to cable aging, for instance, insulation faults happen. This affects the insulation resistance and causes a reduction, whereby an insulation current  $i_{insulation}(t)$

is flowing. This leads to a deterioration of the loss factor and severe hazard situations are the consequence. A graphical representation of a phase diagram chart shows the differences between an ideal and nonideal cable, in which the  $\tan \delta$  as the meaningful quantity to describe the cable quality is illustrated [7].

Using the aforementioned explanations on the VLF generator subject and their measurement principle in assessing the insulation quality the idea of energy recuperation was born.

In terms of energy recuperation, the idea is created to utilize the discharge energy  $E_{vlf,peak}$  in such a way that it can be stored in an intermediate circuit. Concerning the stated problem a technical investigation has to be made. A model-based hardware implementation for giving the first proof of concept for an energy storage system in a very-low frequency high voltage generator application shall be developed.

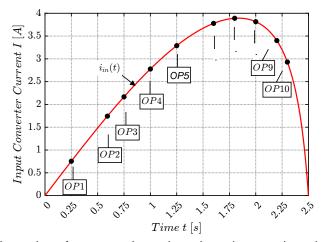

The fundamental consideration for this investigation focuses on Figure 1.2. It can be remarked that during one measurement period  $T_{vlf}$  two discharging phases with the duration  $t_{dis.}=2.5\mathrm{s}$  are present. The provided discharge energy which is covered in yellow in quadrants two and four of the sine wave  $u_{vlf}(t)$  has to be stored.

The maximum discharge energy  $E_{vlf,peak}$  is therefore directly related to the square of the applied voltage since the power cable can be represented as a capacitor. This relation is quantified by the following Equation 1.1.

$$E = \frac{1}{2} \cdot C \cdot U^2 \tag{1.1}$$

The maximum achieved power ratings of the VLF test system are listed in Table 1.1 and have been provided by the company Baur GmbH. These performance data are used throughout the whole thesis as boundary conditions for the design process. The maximum discharge energy is calculated by formula 1.1 and is the main parameter on which the storage type depends. The discharge time is defined as a quarter of the VLF period time  $T_{vlf}$ .

Additionally, during a normal VLF test procedure, ten periods are driven to investigate the tangents delta  $(\tan\delta)$  factor. This procedure is done with different RMS VLF voltage values. If further information about field testing of power cable systems using very-low frequency high voltage signals, the IEEE standard 400.2 is recommended.

So in conclusion the idea was born to develop an energy storage system that intends to functional short-term energy storage system. With regard to the VLF generator, several manipulated variables in the overall VLF system are neglected because of their high complexity. The energy storage system is developed in cooperation with the company Baur GmbH in Sulz. In the first instance, only the charging phase should be defined.

Table 1.1: Maximum performance data of the VLF test system under AC withstand testing

| Symbol               | Meaning                                  | Value         | Unit |

|----------------------|------------------------------------------|---------------|------|

| $U_{vlf,peak}$       | Peak Voltage<br>VLF Generator            | 65            | [kV] |

| $f_{vlf}$            | VLF Frequency                            | 0.1           | [Hz] |

| $\overline{T_{vlf}}$ | VLF Period                               | 10            | [s]  |

| $C_{cable}$          | Maximum Capacitance<br>Power Cable (DUT) | 2             | [µF] |

| $P_{cable,peak}$     | Peak Power                               | $\approx 2.7$ | [kW] |

| $t_{dis}$            | Discharge Time                           | 2.5           | [s]  |

| $E_{vlf,peak}$       | Maximum Discharge<br>Energy              | 4225          | [J]  |

#### 1.2 Motivation

As it is described in Subsection 1.1 an energy storage system for a VLF generator shall be developed. The challenge of the system lies in definitely finding the right energy storage type. In particular, this involves transferring the electrical quantity of electricity into manageable orders of magnitude. The underlying peak power of  $2.7 \mathrm{kW}$  and a short-time energy quantity of 4225J make this task particularly challenging. The interaction of discharge energy and a controlled transfer of the energy flow through a suitable power converter is challenging too. The phased requirements of enabling energy storage with concern of power flow controllability and stability issues will also find their accusation. Based on this, the fundamental question lies in the feasibility of such a system. A concept must be created based on targeted requirements. The question of additional safety concepts and the feed-in after the charging phase are further aspects that can be taken into account in such a system integration. Another question that arises in such an application is the choice of energy storage type. In the applications which are presented in the introduction chapter, one or two common features can be identified when comparing the stated problem with the electrical vehicle utilization. With a first interpretation of the charging phase development, a first statement can be made about whether such high energy storage amounts are possible to store technically.

The motivation of this thesis shall lie in developing a system design concept that should present a proof of concept in terms of a technical manner.

### 1.3 State of the Art

In Chapter 1, an introduction has already been made in which two energy storage system applications are presented.

This section will provide a short review of some technical implementations of ESS.

One type of energy storage is used in an electrical tram system in public transport [4]. Through the use of an On-Board-Energy-Storage-Device (OBESD) which consists of a super-capacitor bank and lithium-ion battery, power dispatcher operation modes like accelerating and moving the tram can be improved. During dwelling at a station, the capacitor bank is connected directly over the contact line to a DC bus. With the use of a bidirectional converter, the capacitor can be charged up again while in later use the lithium-ion battery can be charged.

Another prominent application of an energy storage system is the use of a bidirectional DC/DC converter for incorporating regenerative braking energy. A well-known system in that field of application is the Kinetic-Energy-Recovery-System (KERS) in Formula one cars. Through the use of power electronic methodology, the current power flow of regenerative breaking energy can be absorbed by a supercapacitor bank. The braking energy is stored temporarily in a supercapacitor bank via an intelligent energy conversion network which is comprised of an electric motor and a power electronic unit. The electric drive system is the key element in which kinetic energy is converted to electrical energy. The system charges up the supercapacitor under breaking manoeuvrer and is releasing the same amount of energy under acceleration [8].

A further form and a slightly different form of an energy storage application is presented by Liebherr-Werk GmbH [9], and is called Pactronic. This hybrid power drive concept presents a new millstone for mobile harbour cranes. The system is characterized by a hydraulic energy storage device. The potential energy in this case is stored in an accumulator and can be released on demand. The charging of the accumulator is done by regenerating the reverse power while lowering the load. This system increases the overall efficiency.

All the energy storage technologies which are presented have something in common, namely their structure. In many technologies, a power conversion system and an energy storage type are used. The choice of the energy storage device depends crucially on the application and area of use. The power conversion system is in many utilizations built up to allow a bidirectional power flow. In this short state-of-the-art review, it becomes clear that bidirectional converters together with the energy storage device are the key components. Through the bi-directionality of the converter, the energy storage system enables a flexible power processing interface between the energy saving system and the rest of the system.

# 1.4 Objectives of this Thesis

Inspired by the aforementioned state-of-the-art technologies, which are mostly based on power converter systems and different energy storage types an ESS shall be developed. This thesis aims to present a proof of concept to solve the stated problem. for allowing a technically feasible short-term energy storage system use. The proof of concept shall contain, in the first aspect a design scheme while secondly a final model-based digital controlled hardware implementation on a simulation basis, in Matlab Simulink and Plecs Blockset shall be done. It shall give a closer design insight into which way such large short time-based energy amounts can be technically stored. The cornerstones of this work are definitely the controllability of the power flow from the primary side of the ESS to the secondary side of the storage medium. According to the described technologies in 1.3, the selection of the energy storage type is an enormously important matter and depends mainly on the application and how the energy is available. This work shall therefore investigate different energy storage variants in order to filter out their advantages and disadvantages for the best use case for the stated problem. A technical-based assessment study on a simulation basis with the final digital controlled developed hardware implemented ESS shall be conducted. In this assessment, the current ratings and voltage ratings around and during the charging process shall be verified with respect to controllability and their compliance with electrical component limits. Based on this feasibility study on the subject of energy recuperation in VLF generator systems, it shall be possible to clarify further aspects. This can, for example, be concerning the execution of the system integration, where it still has to be clarified in which way the stored energy is used in later time stamps during the AC withstand test.

# 1.5 System Requirements

Based on the explained problem description in Section 1.1 and the analysis of the state-of-the-art energy storage systems in Section 1.3, a requirement profile could be created in cooperation with the company Baur GmbH.

In this section, a detailed requirement list for the energy storage system is derived to fulfil functionality, electrical parameters, software and energy efficiency. Outgoing from these framework conditions, a concept can be developed to characterize the functionality by a model-based hardware simulation.

The requirements are listed specifically for the respective system groups called

- Energy Storage Type and the

- · Power Converter Topology.

For each group a specific requirement profile is given, which will be presented in Subsection 1.5.1 and 1.5.2. A distinction between a selectable, a mandatory and a requirement itself is made. A selectable requirement has the meaning that a dependency on other requirements is given.

## 1.5.1 Requirements Energy Storage Type

In Table 1.2 the requirements for the energy storage type are listed. It has to be noticed that in terms regarding to a final product design, cost points and volume points are not to be taken into account. The main goal is still in getting the first proof of concept.

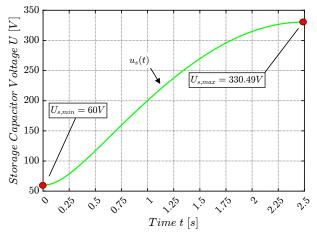

Symbol Meaning Value Unit Type Maximum stored  $\approx 4225$ [J]Requirement  $E_{vlf,peak}$ energy Charge-/ Discharge-time 2.5[s]Requirement  $t_{ch}/t_{dis}$ Lifetime (cycles) Mandatory > 10000nStorage Capacity [F]Selectable  $C_s$ Χ Rated Voltage  $U_s$ 400 [V]Mandatory Storage Capacity  $P_{spec}$ Power density  $[kW/m^3]$ Not Mandatory Χ **Energy density** [Wh/kg] **Not Mandatory**  $E_{spec}$ Χ Storage type > 90%[%]Mandatory  $\mu_s$ cycle efficiency Minimum / Maximum  $\Delta U_s$ 60 - 350[V] Mandatory charging voltage level

Table 1.2: Specification list for the energy storage type

Based on the requirements list, it is clear that electric and electrochemical energy storage systems will be the choice. The storage capacity  $C_s$  is selectable. This means that the capacity of the storage system is depending on the amount of energy  $(E_{vlf,peak})$  that must be stored in one charging process and which voltage difference can be exploited. Charge and discharge time are of significant importance since the overall charge and discharge time are given by a quarter of a full very-low frequency period  $T_{vlf}$ . A minimum and maximum voltage variability  $\Delta U_s$  must be given by the storage process to guide the power flow during the discharge phase into reasonable current ranges. The rated voltage affects the energy acquisition and is coupled in the same way as with the minimum and maximum charging voltage to the discharging power flow. The lifetime properties shall guarantee low maintenance of the energy storage device. Effects like temperature changes and aging of the capacitor are in most cases responsible for capacity losses and can be further investigated in Literature [10].

## 1.5.2 Requirements Converter Topology

The second respective system group is defined as the power converter topology. There are many different types of converters available for different application scenarios [11]. It is therefore vital to get a decision on a specific topology to achieve the desired result. The converter system proposes the management system of power flow between the primary and secondary side of the energy storage system. Thereby, this system forms a power flow control mode that appropriately transfers the power. In Table 1.3 the necessary requirements for the power flow converter are listed. It has to be remarked, that requirements are categorized as desired once, mandatory and requirements themselves. A requirement is specified with a quantity which is measurable like for example the inductor current  $i_L(t)$ .

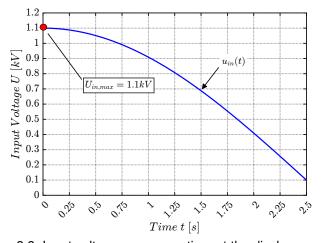

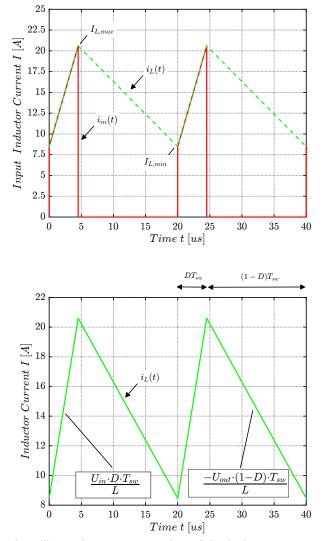

Symbol Meaning Value Unit Type Step-up Step-down Mandatory Χ **Ability** Bidirectional Χ Desired Inductor  $\Delta i_L$ 20 [%]Requirement Ripple Current Switching Frequency 50 [kHz] Requirement  $f_{sw}$ Minimum 100  $U_{in,min}$ [V]Requirement Input Voltage Maximum 1100 [V] Requirement  $U_{in,max}$ Input Voltage CCMConduction Mode Mandatory Average [A]15 - 20Requirement  $I_{L,ave}$ **Inductor Current** Galvanic Isolation Not mandatory

Table 1.3: Specification list for converter topology

# Step-up and Step-down Ability

The converter shall have the capability of stepping up and stepping down the input voltage. Depending on the input voltage on the primary side and the rated power flow it is necessary to provide both functional features. This improves the variability of the power flow control process.

#### **Bidirectional Converter**

In diverse applications, bidirectional power flow DC/DC converters are increasingly employed. In the case of a bidirectional converter sizing and additional components can be reduced to a minimum, due to the fact that the system can operate forward and reverse power flow direction. Furthermore, bidirectional DC/DC converters are one of

the key elements in electrical energy storage systems [11].

#### **Converter Design Specifications**

Further design specifications are the inductor ripple current  $\Delta i_L$ . The inductor defines the energy storing element which transfers electrical energy in specific power flow time stamps to the energy storage type. This causes an indirect effect from the inductor to the output current ripple. So in this way, the system shall operate in continuous conduction mode with an inductor current ripple which is specified by 20% of the maximum mean inductor current  $I_{L,ave,max}$ . By means of the inductor current, the continuous conduction mode CCM shall be implemented. The difference between the continuous conduction mode (CCM) and the discontinuous conduction mode (DCM) of a converter is given by the inductance current characteristics. The CCM is defined to decrease the inductor current ripple in comparison to the DCM. A detailed description of the different conduction modes can be found in [12]. The switching frequency  $f_{sw}$  is set with  $50 \mathrm{kHz}$ , this shall reduce switching losses since high power flows are expected. An appropriate reason for galvanic isolation is not specified. The input voltage and output voltage can share their common ground.

Based on this framework, a conceptual study can be conducted. According to the listed requirements from Section 1.5, the investigation for the desired system design can be made. The technical feasibility shall be in the foreground. The costs and volume points are considered as further optimization points in the second phase of the development process.

#### 1.6 Structure of the Thesis

The structure of this thesis is based on a concept decision phase followed by a detailed system design process and a final system verification. In the conception phase, suitable storage technologies and converter topologies are evaluated. Each system group presents possible solutions to fulfill the requirements. Afterwards, the presented solutions are then independently evaluated through a utility analysis based on evaluation criteria. The solution with the highest overall score is then used for the further system design. In the following chapters afterwards, the system design process as well as its model-based hardware implementation is shown. The system design process forms recurring dependencies between different system groups as well as a calculation that is highly dependent on theory. Finally, the energy storage system is evaluated and verified to obtain a statement about its feasibility.

# 2 Concept

According to the stated problem in Section 1.1 the conceptual design phase is divided into two major subgroups, called energy storage type and converter topology. In this chapter, the first part concentrates on defining and selecting an appropriate choice of an energy storage device according to the requirements in Subsection 1.5.1. In the second half, suitable converter topologies are analyzed and evaluated with regard to the requirements from Subsection 1.5.2. Based on a utility analysis the most promising topology is used.

# 2.1 Selection of Suitable Energy Storage

To ensure the mechanism of storing energy from the VLF power path, a suitable storage device is required.

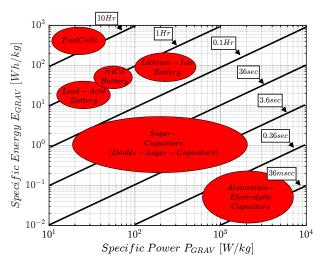

For this purpose, the Ragone diagram in Figure 2.1 is primarily used as a visualization for comparing different energy storage technologies. The Ragone diagram presents the storage device energy density versus the power density on a double logarithmic representation. The main diagonals in this figure illustrates the charging and discharging times [13], [14].

Figure 2.1: Incorporation of energy storage devices in the Ragone diagram reproduced from [2]

With the use of the Ragone diagram a better thorough understanding of the energy

storage type can be given in terms of power and energy ratings, as well as charge and discharge times.

To reduce the choice of energy storage types, only electrochemical and electrical storage variants are elaborated in this context, since the available energy is of electrical quantity. In a more detailed analysis of the presented Ragone diagram and under consideration of the storage requirements from Subsection 1.5.1, it can be seen that due to long charge and discharge times, batteries are out of specification and therefore they are not suitable for the desired application. This leads ongoing to an extensive elaboration on aluminium electrolytic capacitors and supercapacitors. According to the following evaluation criteria in Subsection 2.1.1 the elaboration of aluminium electrolytic capacitors and supercapacitors is conducted. Through a final utility analysis, the most promising storage device is chosen for further system design.

#### 2.1.1 Evaluation Criteria

With the aid of the below-listed evaluation criteria, the supercapacitor and aluminium electrolytic capacitor storage variants are investigated. These evaluation criteria shall help to meet the appropriate storage system choice.

- Charge- / discharge time: The requirements show that a high amount of energy must be absorbed by the energy storage system in a short period of time. Short and fast charging and discharging times are preferable.

- Charge / discharge cycles: During charge and discharge periods complex reactions happen. In batteries for example chemical reactions are caused due to charge and discharge procedures. This can give an impact on the performance and can minimize energy storage capacity [10]. During an AC-Withstand test with a VLF system, many charging and discharging cycles are expected.

- **Lifetime:** The number of charge and discharge cycles as well as temperature dependency influence the lifetime of the storage system and can cause a reduction of the capacity.

- **Power density:** Describes the energy transfer rate per unit volume or mass of an energy storage system.

- Energy density: Describes the energy which is accumulated per unit volume or mass.

- Rated Voltage: The rated voltage criteria define the voltage variability of an electrical energy storage device. Due to the expected high power ratings of  $2.7 \mathrm{kW}$  during the power cables discharge phase an increased voltage variation is preferred.

- Equivalent Series Resistor ( $R_{ESR}$ ): The serial equivalent internal resistance  $R_{ESR,C}$  determine the self-heating of the energy storage device. A small ESR is also preferable here in order to lower dissipation losses.

In the following Subsections 2.1.2 and 2.1.3, the analysis of those storage systems that have been identified as shortlisted is performed.

## 2.1.2 Aluminium Electrolytic Capacitor

AS one of the most direct ways of storing electrical energy is done by using capacitors. Typical capacitors are aluminium electrolytic capacitors (AEC), ceramic capacitors and tantalum capacitors. These types of capacitors collect and store charges on the plane electrodes.

The capacitance of typical capacitors is built up through two plane electrodes which are isolated through a dielectric material. So in this case capacitance values are ranging from single micro farad up to milli farads. In comparison to supercapacitors their capacitance per unit volume is much lower but their rated operating voltages are around 300 times greater. Especially in applications where the total capacitance is in the medium capacitance range and the rated voltage has to be in a higher volt range makes them suitable for it.

The charge and discharge times of conventional capacitors are typically in the range of picoseconds to milliseconds, while the charge times of super capacitors are in the range of milliseconds to seconds with Reference to [14]. In comparison, batteries have a lower charging power compared to capacitors, which leads to a longer charging time. Due to their high energy density, batteries are able to supply energy over a longer period of time instead of conventional capacitors. Capacities, however, provide a high power density in short time periods.

The charge and discharge capability of conventional capacitors and supercapacitors ranges around a million cycle life states. With regard to this assertion, batteries are reduced in their cycle life by a factor of about 250 compared to capacitors. Another measurement that is directly associated with the charge and discharge process is the resulting efficiency. The overall charge/discharge efficiency for a conventional capacitor ranges at around 95 %, while batteries have values in the range of 70 to 85 %, with accordance to [15].

In comparison to supercapacitors, aluminium electrolytic capacitors have cell voltages that are 300 times greater. In this case, no worries about equalization circuits for voltage balancing of a capacitor module have been taken into account. This reduces the circuitry effort tremendously and makes them easier to install.

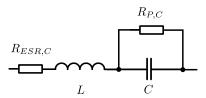

Another important aspect is the operating temperature range capability. Typical charging temperatures for conventional capacitors are ranging from  $-20^{\circ}$  to  $125^{\circ}$ . Supercapacitors temperature range is on the magnitude base of  $-40^{\circ}$  to approximately  $65^{\circ}$ . Due to the equivalent series resistor, additional energy losses contribute to the system and affect the internal temperature. A better inside view of this subject gives the equivalent circuit model of a capacitor in Figure 2.2. This simplified model represents a first-order

circuit model, which consists of four circuit components. In the current consideration, the inductance L is neglected because it is usually small. During the charging and discharging processes the equivalent series resistance (ESR)  $R_{ESR,C}$  contributes mainly to the energy losses ( $P_{loss,C} = I^2 \cdot R_{ESR,C}$ ) and in further consequence a temperature rise occurs.

Figure 2.2: First-order equivalent circuit model of a conventional capacitor

The parallel Resistor on the other side  $R_{P,C}$  simulates mainly those energy losses due to self-discharging. This resistor is also often referred to as the leakage current resistance. So in a real capacitor, the Resistor  $R_{P,C}$  is always much greater than the  $R_{ESR,C}$ . In a typical energy storage application, capacitors as an energy storage system are connected in series or in parallel to build up a module in order to fulfill the design requirements.

In Equation 3.4 the total capacitance  $C_{Total}$  and the total equivalent series resistance  $R_{Total}$  of the designed storage capacitor module is given.

$$C_{Total} = C_{cell} \cdot \frac{m}{n}$$

$R_{Total} = R_{Cell} \cdot \frac{n}{m}$  (2.1)

The abbreviations n and m describe the number of series cells and the number of branches that must be in parallel connection.  $C_{Cell}$  and  $R_{Cell}$  represent the total capacitance and equivalent resistor of the capacitor storage bank. Besides the power losses explanation that occurs a time-based characteristic quantity is derived. The response time constant ( $\tau_C = R_{ESR,C} \cdot C$ ) in an aluminium electrolytic capacitor is about  $\approxeq 10^{-4}$  whereas in supercapacitor usually a longer response has to be expected. For further information about parasitic model parameter extraction on capacitors as well as an expanded side-by-side energy storage technology comparison, it can be referenced on [16].

# 2.1.3 Supercapacitor

In addition to the Ragone diagram in Section 2.1, it can be stated that supercapacitors are placed in terms of energy and power density between batteries and conventional capacitors. Supercapacitors are also known under vernacular names such as power capacitors, electrochemical-double-layer capacitors (EDLC) or ultracapacitors (UCaps). These storage types feature long life, high power capabilities and have capacitances of several order of magnitude, due to their internal structure [17]. In this

way these capacitors are also referred as electrochemical capacitors which make them similar to batteries. A further description of the internal structure can be found in Literature [14], where also a comparison review against aluminium electrolytic capacitor is presented.

Supercapacitors are nowadays available in sizes up to several hundred farads per unit but only have voltage ratings of 2.3 to 3.3 V per cell. In terms of their functionality supercapacitors are governed by the same principels as conventional capacitors. The only difference are in their internal structure. A much higher surface area and their thinner dielectric material provide high capacitance[18].

Their ability to be charged and discharged in a matter of a few seconds determines the feasibility of their use in a particular application like [4]. With these characteristic time properties, fast recharging can be managed. Additionally, the power delivery is 10 to 25 magnitudes greater, than compared to batteries [19]. For further actual review information about important features and limitations of batteries, supercapacitors and conventional capacitors, Table 1 in Literature [2] is recommended. Always depending on the internal structure of the supercapacitor, or double-layer capacitors offer an energy density that is 10 to 100 times bigger than conventional capacitors.

In comparison to lithium-ion batteries, supercapacitors point out by long cycle life, in the magnitude of order 500 times higher. Directly compared to conventional capacitors no major quantity difference is given between these two topologies. The cycle life as mentioned before is also affected by the temperature. In UCaps and conventional capacitors these temperature ranges are defined, in accordance to Literature [2] between the range of -40 to  $70^{\circ}\mathrm{C}$  and -20 to  $125^{\circ}\mathrm{C}$ , whereas in batteries temperatures of 0 to  $45^{\circ}\mathrm{C}$  are normal during charging.

To guarantee an adequate life expectancy of a supercacpacitor module, active or passive balancing circuits have to be considered to minimize differences in cell voltages. Especially care must be taken when ultracapacitors are connected in a string since each individual cell cannot exceed the maximum proposed cell voltage. In a further consequence, this can lead to permanent damage. In Literature [19] a comprehensive review on supercapacitor and their applications and developments as well as equalization circuit strategies are presented and explained in a much more detailed fashion.

In Table 2.1 a useful comparison between an ultracapacitor with a representative lithium-ion cell and an aluminium electrolytic capacitor is done to get a better inside into all those mentioned characteristic quantities.

Table 2.1: Comparison of ultracapacitor with lithium-ion cell and aluminium electrolytic capacitor

| Attribute                                                            | Ultracapacitor<br>BCAP0350               | Lithium-lon<br>18650 cell                           | Aluminium-<br>Electrolytic-<br>Capacitor<br>ALS71H203QT400 |

|----------------------------------------------------------------------|------------------------------------------|-----------------------------------------------------|------------------------------------------------------------|

| Capacitance                                                          | 350F                                     | 2.1A h                                              | 20mF                                                       |

| Voltage                                                              | 2.7V                                     | 3.6V                                                | 400V                                                       |

| Resistance                                                           | $3.2 \mathrm{m}\Omega$                   | $75 \mathrm{m}\Omega$                               | $12 \mathrm{m}\Omega$                                      |

| Mass                                                                 | 63g                                      | 70g                                                 | 2kg                                                        |

| Volume                                                               | $5.3e^{-5} \text{m}^3$                   | $1.7\mathrm{m}^3$                                   | $5.5e^{-3}$ m <sup>3</sup>                                 |

| Cycles                                                               | > 500000                                 | < 2000                                              | > 500000                                                   |

| Peak<br>Energy                                                       | $E_{UC} = \frac{C \cdot U^2}{7200}$      | $E_{Li} = C \cdot U_{OC}$                           | $E_{AEC} = \frac{C \cdot U^2}{7200}$                       |

| Peak<br>Power                                                        | $P_{pk} = \frac{U^2}{4 \cdot R_{ESR,C}}$ | $P_{pk} = \frac{2 \cdot U_{OC}^2}{9 \cdot R_{int}}$ | $P_{pk} = \frac{U^2}{10 \cdot R_{ESR,C}}$                  |

| $\begin{array}{c} \hline \\ \text{Peak Power} \\ P_{pk} \end{array}$ | 569.53W                                  | 38.4W                                               | $1.3e^6\mathrm{W}$                                         |

| Peak Energy $E_{pk}$                                                 | 0.354W h                                 | 7.56W h                                             | 0.222W h                                                   |

| Specific<br>Energy<br>Density                                        | $5.62 \mathrm{Wh/kg}$                    | $108 \mathrm{Wh/kg}$                                | $0.11 \mathrm{Wh/kg}$                                      |

| Charge Temperature<br>Range                                          | $-40$ to $65^{\circ}\mathrm{C}$          | 0 to 45°C                                           | −40 to 85°C                                                |

# 2.2 Utility Analysis

In the previous Section 2.1, suitable storage topologies are presented. The selection of these storage topologies results from the need to achieve fast charging and discharging times and to meet the requirements to temporarily store the discharged energy over a defined voltage range. This section compares finally the presented topologies. In Table 2.2 the utility analysis is shown. In the utility analysis, points are awarded from one to ten. Even though batteries were initially excluded, it was decided to include them in the evaluation as well to significantly show the differences.

Table 2.2: Comparison of the presented electrical storage topologies

| Storage<br>Topologies                     | Rated Cell Capacitance $C$ $[F]$ | Rated Cell Voltage $U_{Cell}\left[ \mathrm{V}  ight]$ | Charge-<br>Discharge-Times $t_{c,dc}\left[\mathrm{s} ight]$ | $\begin{array}{c} {\sf Charge-} \\ {\sf Discharge-Cycles} \\ n \ [ \ ] \end{array}$ | Temperature Range $\Delta T  [{ m K}]$ | Peripherals | Total<br>Points |

|-------------------------------------------|----------------------------------|-------------------------------------------------------|-------------------------------------------------------------|-------------------------------------------------------------------------------------|----------------------------------------|-------------|-----------------|

| Batterie<br>LI-Ion                        | -                                | က                                                     | -                                                           | ဇ                                                                                   | 9                                      | 2           | 16              |

| Aluminium-<br>Electrolytic-<br>Capacitors | 4                                | 8                                                     | 6                                                           | 6                                                                                   | 7                                      | 7           | 44              |

| Supercapacitors                           | 10                               | 3                                                     | 7                                                           | 6                                                                                   | 9                                      | 5           | 40              |

The result of the utility analysis shows that the aluminum electrolytic variant is the most suitable form of energy storage. With regard to the aluminium electrolytic capacitor and its rated capacitance and the rated cell voltage (compared to the supercapacitor) an overall higher score is reached than compared to the super capacitors. The low effort of cell balancing techniques and their fast charge and discharge times affirm them as a suitable choice for the desired power application.

For the remaining topologies like supercapacitors and batteries, no further investigation has to be made. In comparison to the charge and discharge cycles of the supercapacitors lower cycle lifes will be achieved with batteries. Furthermore, long charge and discharge times do not make them an appropriate choice of use, since the energy storage has to be done in less than three seconds, as it is mentioned in Section 1.1.

With a further look at the power and energy transmission, the supercapacitor variant can be a promising alternative too. However, a certain voltage variability must be present in the case of providing manageable charging currents. Finally, the converter topology has to be able to handle the charging currents. Another major drawback behind supercapacitors is their series composed module structure to generate higher total voltage ratings.

Based on this utility analysis, the aluminium electrolytic capacitor variant will be further considered in the system design process.

# 2.2.1 Summary Energy Storage System

In this section, the most promising concept was selected from the three electrical storage topologies, which are evaluated by using evaluation criteria. It was specifically stated that due to changing energy forms additional losses occurs, and only those storage technologies are to be considered that work in the electrical domain. So in that case, the most important properties of the electrical and electrochemical storage topologies are compared against each other by using the Ragone diagram. Subsequently, then the energy storage topologies are explained with respect to rated capacitance, rated operating voltage, charge and discharge times and other characteristic quantities. After that, based on the system requirements and the aim of a predevelopment, the storage systems are utilized against each other. It must be noticed, that this concept phase does not consider cost points and volume points. Through the defined energy storage system a first design of the storage system can be made. In the further course of the concept phase, the appropriate converter topology is identified.

# 2.3 Selection of a DC/DC Converter Topology

Various DC/DC converters with interleaved technology or bidirectional capability are getting more and more attention [20]. Especially bidirectional converters are a preferred choice in energy storage systems. With regard to this, they provide the ability to control the power flow in either forward or backward directions.

In this section, various possible circuit topologies will be examined and compared with each other. On the basis of evaluation criteria, the most promising concept is chosen. Based on the choice of the circuit topology, the system design is carried out.

With the assistance of the converter requirements from Subsection 1.5.2 following important aspects must be considered to narrow the search for power converters:

#### Topology:

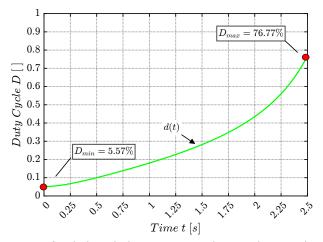

Due to the specification that the input voltage is not constant and drops during the discharge phase similar to a quarter period of a sinusoidal voltage, the converter must operate as a step-down or step-up converter, depending on the charging voltage at the energy storage device. For this reason, a converter with the ability to stepping-up and stepping-out have to be preferred.

#### · Galvanic Isolation:

Galvanic insulation is not mandatory. Non-isolated DC/DC converters are the preferred choice of us because it allows current flow directly from input to output. This reduces complexity, size and price.

#### Operation mode:

The converter shall operate in continuous conduction mode (CCM) throughout the discharge cycle. During this switching mode, the converter has to be capable to work as a buck, boost or a buck-boost converter.

#### Transmission Rate:

The minimum and maximum transmission ratios of the converter shall not be exceeded. Instability issues during power flow conversion due to oscillation have to be avoided. The actuating variables (duty cycle) are limited to the lower 5% and the upper 95% of the duty cycle.

#### 2.3.1 Evaluation Criteria DC/DC Converter

In order to finally enable a comparison between suitable topologies, evaluation criteria have to be defined. Assessments regarding assemblies volume of the converter topology are not considered. The aim of the evaluation is to find a circuit variant for the depicted problem from Section 1.1. The objectives are to fulfill the requirements from Subsection 1.5.2. The main criteria are therefore the ability to drive the power converter in buck, boost or mandatory in buck-boost mode. The following list presents the evaluation criteria:

## Amount of components:

The main objective is to solve electrical issues with less components. This reduces complexity, and bulkiness and allows a simpler circuit design. Especially the number of components for the power section, as for instance the number of inductors, transformers, switches or diodes significantly determine the topology and characteristics of the converter.

#### Operationability:

Operability defines whether it is possible to work in different conversion directions. That means, is the underlying topology able to work in Buck, Boost or Buck-Boost mode depending on the input and output voltage condition.

#### Industrialization:

Under this criterion, the technical feasibility of the converter topology should be considered. Those topologies that have proven themselves in various applications are to be preferred.

#### Peripherie:

This evaluation criterion shall take into account the additional effort which must be taken to drive the semiconductor circuits effectively.

#### Voltage at the switches:

The occurring voltage at the semiconductor switches has a direct effect on the losses. It follows that the semiconductor switches must have a certain electric strength. The total losses of the semiconductor during switching on and off must be analyzed.

In the next Subsections 2.3.2, 2.3.3 and 2.3.4 suitable converter topologies are presented.

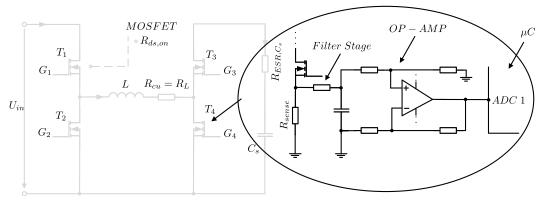

## 2.3.2 Synchronous Buck-Boost Converter

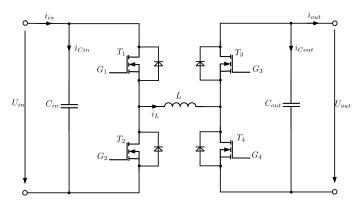

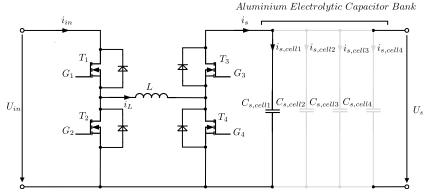

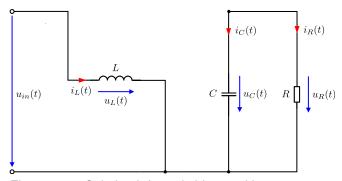

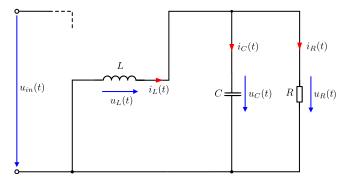

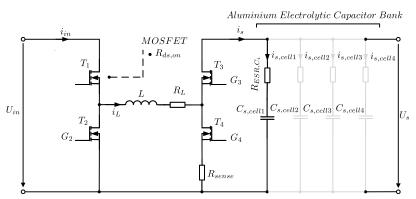

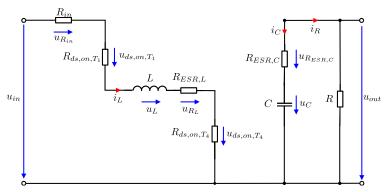

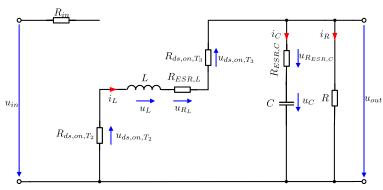

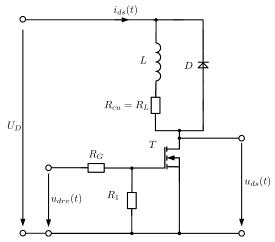

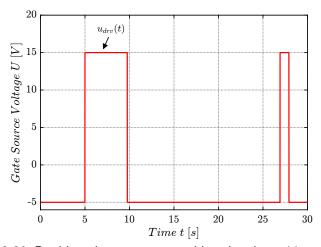

In Figure 2.3 the circuit topology for a synchronous buck-boost converter is illustrated. This figure represents two combined converter types: On the hand, the buck converter is presented and on the other hand the boost converter. This converter topology has already been discussed and explained in detail in various technical Literature [21], [20]. For this reason, a detailed description will not be given and only a summary of the most important findings from the literature will be presented.

Figure 2.3: Circuit topology of a synchronous buck-boost converter in a H-Bridge configuration

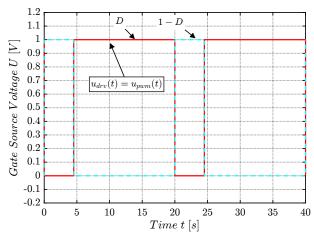

This topology is derived from the non-inverting buck-boost converter. It is built up symmetrically. As explained, the circuit topology is achieved through a cascaded arrangement of a buck and boost converter. The representative diodes of the non-inverting buck-boost topology are replaced through active switching elements. With this replacement, a 4-quadrant operation technique is possible and hence this topology allows energy flow in both directions. Due to this bidirectional power flow is enabled. The buck-boost is implemented in an H-Bridge topology and has an adaptive architecture where it can operate in one of the three modes called a buck, boost or a buck-boost depending on the input to output voltage ratio. In Literature [22] a table of the switching states of the MOSFET switches  $T_1$ ,  $T_2$ ,  $T_3$  and  $T_4$  is shown to execute the different converter modes.

In its H-Bridge configuration, the synchronous buck-boost converter only requires one single inductor L. Some advantages are that less passive components are in use, high flexibility is guaranteed and high efficiency in high and low power conversion areas can be given.

All in all, this makes the system most versatile but also brings drawbacks with it. One of the major drawbacks is definitely the number of switches, which affects switching losses. More complexer control algorithms and more turn-on losses because of reverse recovery problems of the transistors body diodes will also occur. In the case of the use of NMOS transistors as high-side switches, a charge pump is needed. Through this, a sufficient gate drive voltage has to be established. As a consequence, this makes the control system and control algorithm of the semiconductor switches somehow complex.

The use of a half-bridge driver with internal bootstrapping allows the control of the high-side MOSFET. A further opportunity for reducing the effects of this problem is to use transistors with low gate-source voltage threshold values. For more investigations concerning the integration of NMOS technology in a H-Bridge the above literature is recommended.

Furthermore, it can be stated that this topology uses only one inductor to transfer energy from the primary side to the secondary side. This results in higher efficiency when compared with a combined half-bridge converter (CHB) [23].

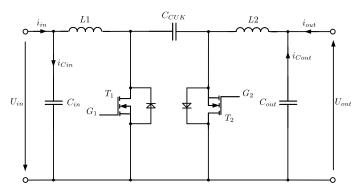

#### 2.3.3 Cuk - Converter

The Cuk converter topology is presented in Figure 2.4. The key elements in this circuit are the two inductors  $L_1$  and  $L_2$  at the input and output.

Figure 2.4: Circuit topology of a bidirectional Cuk-Converter

Detailed explanations of this topology can be found in [21], [1], [24], [25]. The findings are presented in the description below.

The bidirectional Cuk is derived from the unidirectional Cuk converter by replacing its diode through a power MOSFET. In its configuration, it inverts the output voltage and can either increase or decrease the input voltage  $U_{in}$ . By slightly adjustments of the inductors  $L_1$  and  $L_2$  very small input and output current ripple can be achieved. This is a significant advantage over other inverting topologies such as flyback converter and buck-boost converter. By winding both inductors on the same core the Cuk converter can be optimized in size and considerably eases the requirement profile. Another advantage of this circuit is the straightforward control of the semiconductors  $T_1$  and  $T_2$ , where only simple drive circuits due to the low-side MOSFETs can be used. In the same way, as with all converter types, the inductance is used as an energy storage element during the switching phases. The conversion ratio  $M_{CUK}$  can vary between the ranges of minus infinity and zero. Additionally, the Cuk converter is inherently unstable when the output current is controlled. If the input current is uncontrolled this can lead to an undamped oscillation between  $L_1$  and  $C_1$ . This results than in excessively high voltages across  $C_1$ . In order to prevent these oscillations, an additional damping circuit has to be applied. Another disadvantage is that more reactive components are in use. Furthermore, the  $C_{cuk}$  couple capacitance have to be greater than the input voltage, which provides a limitation in choice. All in all this converter topology is suited for applications like battery equalization, hybrid supercapacitor batterie interfaces and bidirectional power flow management systems [26].

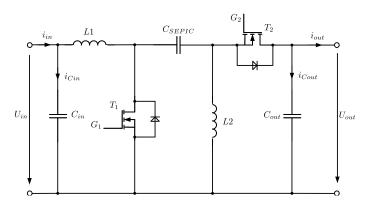

#### 2.3.4 Sepic - Converter

Basically, this topology from Figure 2.5 is called Sepic converter, which looks quite similar to the above mentioned Cuk converter. The only difference is that MOSFET  $T_2$  and inductor  $L_2$  are rearranged. This converter topology has already been investigated in the Literature [27], [28]. The findings are presented below.

Figure 2.5: Circuit topology of a bidirectional Sepic/Zeta-Converter

The Sepic converter is a buck-boost converter type. This topology includes two power switch  $(T_1,T_2)$ , two inductors  $(L_1,L_2)$  and two capacitors  $(C_{SEPIC},C_{out})$ . The unidirectional Sepic converter can be converted to a bidirectional Sepic converter by replacing the unidirectional switch with a bidirectional switch called MOSFET. Also here the inductors L1 and L2 can be coupled in order to reduce current ripple, voltage ripple and therefore the voltage stress on the switches. Through the rearrangement of the aforementioned components the Sepic converter obtain a positive output voltage. In theory, the conversion ratio  $M_{SEPIC}$  can vary between zero and infinity.

The coupling capacitor has the functionality of blocking any DC current path between input and output lines. Besides this, an adverse effect is definitely the more complex and therefore more vulnerable control of switch  $T_2$  compared to the Cuk converter. Another drawback is that especially the  $C_{SEPIC}$  capacitance must have DC voltage ratings that is greater then the maximum input voltage. The dimension of  $L_1$  and  $L_2$  can be chosen to be equal. Moreover, ceramic capacitors are the preferred choice of coupling capacitors, due to the ability of handle large root-mean-square currents. The coupling capacitor  $C_{SEPIC}$  selection depends on the root-mean-square current. Due to a mismatch of a selected coupling capacitor  $C_{SEPIC}$  oscillation and in further consequence instability issues happens. In order to solve stability problems, a damping branch has to be placed in parallel to the coupling capacitor to increase controllability. In this way, lower ceramic capacitance value can be chosen and the damping branch can be build up by low cost electrolytic capacitors.

## 2.3.5 Utility Analysis DC/DC Converter

Outgoing from the findings of the presented bidirectional DC/DC voltage converter systems analysis is made. In Table 2.3 the comparison of the presented topologies through a utility analysis is shown on the next page.

### 2.3.6 Summary Converter System

The utility analysis from Subsection 2.3.5 has shown that the synchronous buck-boost converter is the choice of use for the further system design. The decision is based in particular on its positive aspects. On the one hand, through its H-Bridge implementation, it can be used in a wide variety of applications and thus brings with it a high degree of industrialization, while on the other hand high flexibility is guaranteed. The system allows for instance operations in buck, boost or buck-boost mode depending on the input to the output voltage. This capability leads to the positive effect of reducing switching losses, as the system can operate as a buck or boost converter during power flow control. In comparison to the Cuk and Sepic converter less passive components have to be used, whereas a higher efficiency in high power conversions will be achievable. The only disadvantage that can be noted is the control of the high-side switches.

Cuk and Sepic present alternative forms of bidirectional buck-boost converters. They gain positive aspects with their low ripple current at the input and output. However, these positive effects are not outweighed by the fact that almost two equally large storage inductances are required. Due to the expected high current ratings during the discharge phase, it is assumed that the electrical component arrangement will be very difficult to realize. Another major adverse effect is the number of passive components and their dissipation losses.

Table 2.3: Comparison of the presented bidirectional DC/DC converter

| Converter<br>Topologies                 |   | Amou            | Amount of<br>Components |   | Operation- Industri-<br>Mode alization | Industri-<br>alization | Peripherie | Voltage at<br>the Switches | Total<br>Points |

|-----------------------------------------|---|-----------------|-------------------------|---|----------------------------------------|------------------------|------------|----------------------------|-----------------|

|                                         | T | L $C$ $R$ $T$   | R                       | L |                                        |                        |            |                            |                 |

| Snychronuous<br>buck-boost<br>converter | - | N               | 2 0 4                   | 4 | 10                                     | თ                      |            | 9                          | 35              |

| Cuk<br>converter                        | 0 | 2 3 (4) 0 (1) 2 | 0 (1)                   | 7 | က                                      | 5                      | ∞          | 5                          | 28              |

| Sepic<br>converter                      | 7 | 2 3 (4) 0 (1) 2 | 0 (1)                   | 2 | 4                                      | 5                      | 5          | 9                          | 27              |

## 2.3.7 Summary Concept Phase

In this chapter, the main effort was to get a thorough knowledge of energy storage types and DC-DC converter topologies. Outgoing from the requirements for both subsystems, a representation of the most common findings of the literature is presented. By using this investigation a utility analysis is made in order to find the particular system assembly to solve the stated problem. In this way, the aluminium electrolytic capacitor is selected as an energy storage unit. The main advantages are the high voltage ratings combined with the low effort of building up a capacitor bank. In addition, they are well suited for high ripple currents but due to their size and form-factor, they achieve very low energy density levels. The second key component is the power conversion converter. In an analogue way as with the energy storage system, the converter topology is chosen in accordance to fulfil the specified requirements, see Subsection 1.5.2. With the aid of the utility analysis, the synchronous buck-boost converter is the preferred choice for an extended system design. This decision is covered by the positive effects that the converter shines with high operation mode ability, less passive components and high efficiency in high power conversion applications. In the ongoing next Chapter 3 the complete system design process is conducted. In the first design stage, the energy storage unit will be defined and composed while in further steps an analytic calculation of the energy storage system process is made. Further the converter will be dimensioned and analysed based on static and dynamic analysis approaches.

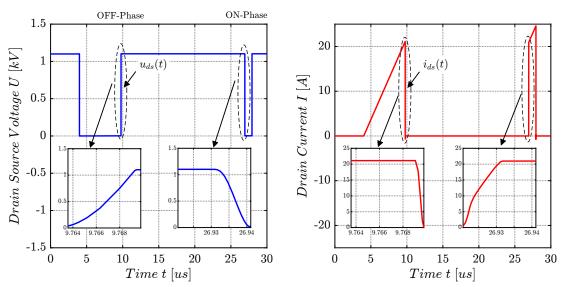

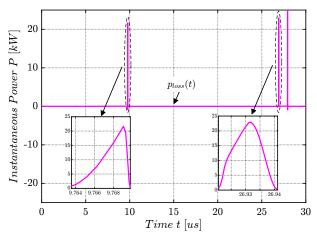

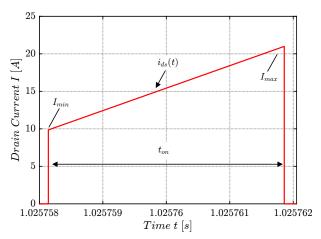

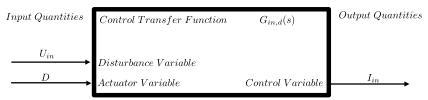

# 3 System Design